Timing analysis is used to calculate the total delay of a circuit that uses flip-flops considering its various propagation delays for each point in the circuit.

Imagine that we wish to calculate the maximum clock frequency of a circuit , and determine if the circuit have any hold time violations. We first need to know some information that is usually in the specification of each chip, since it depends on the materials used and the logic arrangement of the logic gates.

In order to calculate the maximum clock frequency we always have to consider the longest and slowest path of the circuit that uses flip-flops. To determine hold time violations, we have to consider the shortest and faster path.

In general we consider for each gate if no further information is given. The value of is usually represented by an interval, to calculate the maximum clock frequency we always use the max of that interval, to determine time violations we have to consider the minimun of that interval.

Given that information, we can calculate the minimum time that the clock cycle can have without compromising the functionality of the circuit (losing signals due to delay etc).

To determine hold time violations, we check the following:

If thats true, then the signal have enough time to keep output stable. If thats false, then the circuit has a hold time violation.

Example:

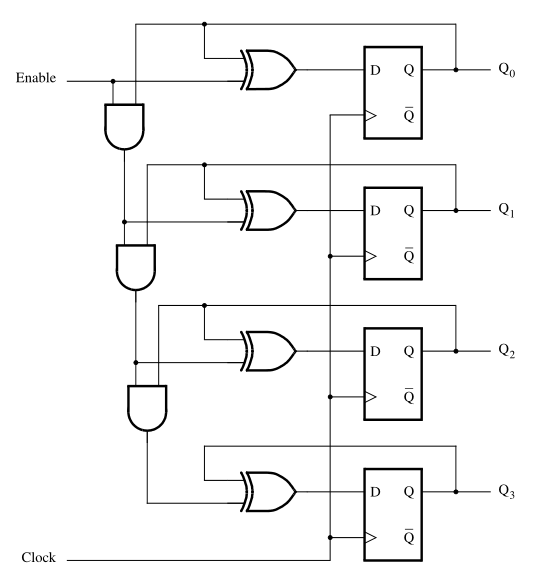

We desire to calculate the maximum clock frequency and determine the existence of any hold time violations on the following circuit:

Considering the longest path, we have the following:

Considering the shortest path, we have the following:

So there is no hold time violations on the circuit.

Clock skew

Sometimes we have a delay in the arrival of clock in only one point of the circuit, we call that delay time . The clock skew has the effect of reducing the delay of that part of the circuit, because it provides aditional time before data is loaded into the flip-flop. So we have the following:

This can change the critical path of the circuit that we choose to calculate the maximum frequency, so we have to pay very close attention to that. Another effect is that the hold time is increased: